Hi Welcome to ChipNCode Blog,

In this Blog Series we will be going to explore about STM32 Driver Development along with ARM Cortex M Internal Details. I like to keep the blog simple and wanted information and easy to understand.

In today’s blog we will see STM32F4 Memory Map and Bus Interfaces

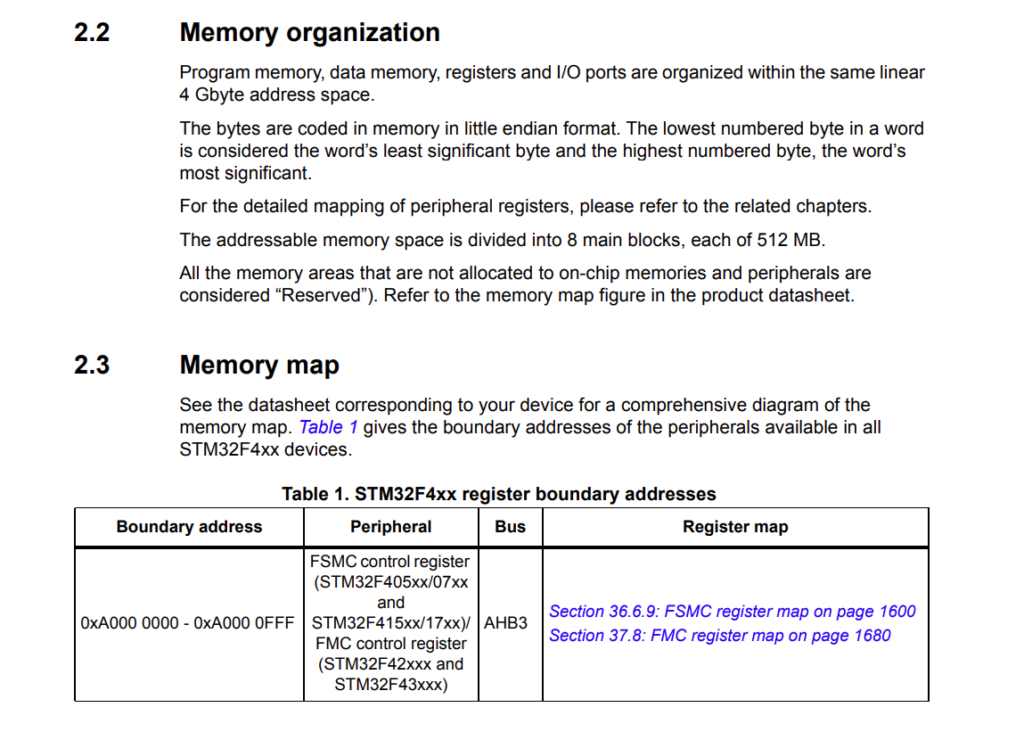

STM32F4 Memory Map

- Processor: ARM Cortex M4

- System Bus: 32bits

- ARM Processor can support upto 2^32 of different address i.e. 4GB 0x0000_0000 to 0xffff_ffff

- Basically based on the producer such as STMirco electronics and TI and so on, all will use between these address to store and access the peripherals

- For example, GPIO, I2C and SPI registers will be available between these addresses

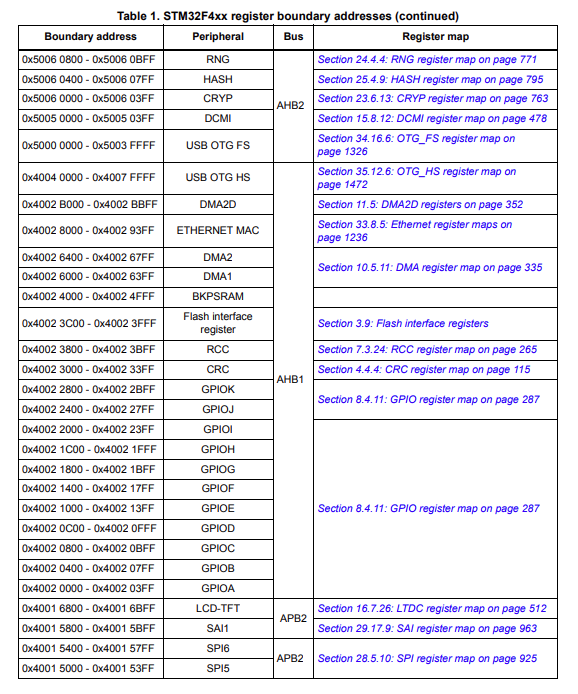

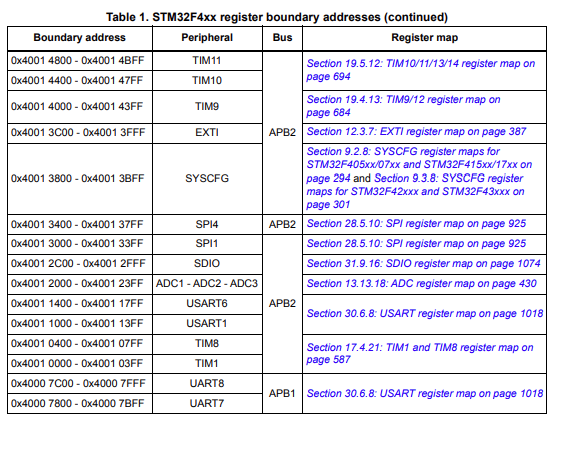

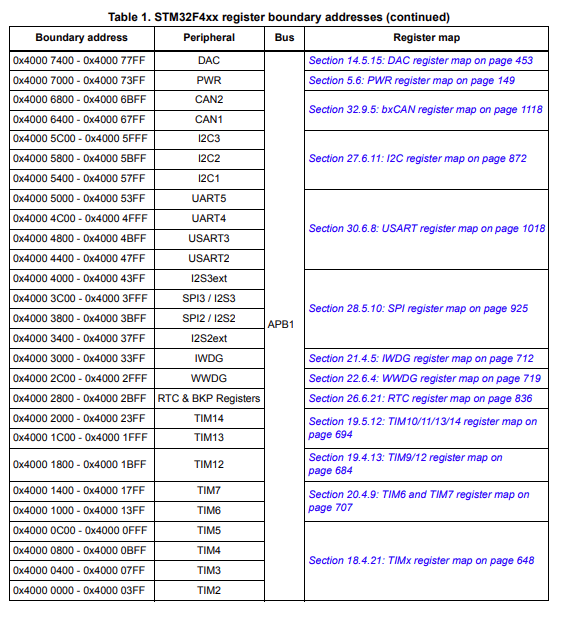

- In STM32F4 Series controller, if we see 0x4002_0000 range having to configure GPIOn peripheral and these supported registers will be available in this address. Note: this addreess selection will be based controller manufacturer

- Mainly, AHB and APB Buses available and some of the address range and some peripheral will be connected in AHB bus and some peripheral will be connected to APB Bus.

- AHB has AHB1, AHB2 AHB3 so on and APB has APB1, APB2

Memory Organization and Memory Map

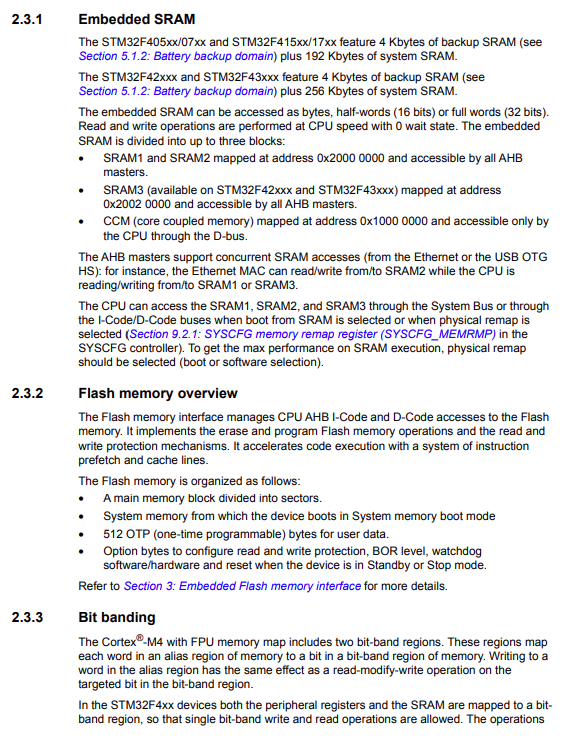

FLASH and SRAM Memory

Flash Memory starts from 0x0800_0000 to 0x1FFF_FFFF

SRAM Memory Starts from 0x2000_0000 and size of SRAM is depends on the controller using and accessible by AHB Bus

Reference

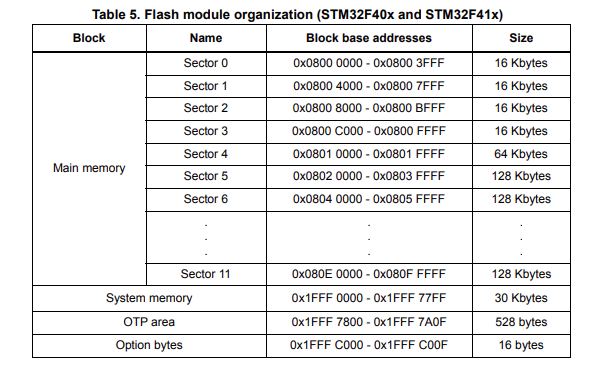

STM32F446 Bus Interface

- STM32F4 series is run by ARM cortex m4 bus

- In STM32F446x controller is running at 180 MHz

- In General, Microcontroller having processor inside along with FLASH, SRAM and Other Peripherals and communications between processor and any of the peripherals along with memory will happen via BUS

- Here, ARM Cortex M4 has 3 bus

- I-BUS: Instruction Bus

- D-BUS: Data Bus

- S-BUS: System Bus

- Basically, Processor will communicate with FLASH via AHB Bus Matrix here

- I-BUS/ICODE:

- Is used to fetch the instruction from the flash memory and run the processor and taken the action based on the instructions

- Instruction fetches from Code memory space 0x0000_0000 to 0x1FFF_FFFC are performed over 32bit AHB-Lite bus

- D-BUS/DCode:

- whenever the const variable is stored inside the flash and needed to communicate between SRAM, it uses Data bus to fetch the data values from the FLASH or SRAM

- Data and Debug access to code memory space, 0x0000_0000 to 0x1FFF_FFFF are performed over 32bit AHB-Lite bus

- Core data having first piriority then once bus release then debug priority will be there

- S-BUS/System:

- Instruction fetches and data and debug access to address range 0x2000_0000 to 0xDFFF_FFFF and 0xE010_0000 to 0xFFFF_FFFF are performed over 32bity AHB-Lite bus

- Also name system is used because if we see all the GPIO, Peripherals and RCC etc all the things which are allocated in the memory sections allocated after the 0x2000_0000 here IBUS and DBUS no access. only System bus having access

- I-BUS/ICODE:

STM32F446xC/E Block Diagram

AHB and APB Interfaces

- AHB Stands for Advanced High Performance Bus

- APB Stands for Adavanced Peripheral Bus

There are AHB1 and AHB2 and AHB3 protocols available all these come from AHB bus matrix

AHB – Runs at higher frequency and APB is slower compared

AHB protocol is divided into Two Sub Buses

- AHB/APB1

- AHB/APB2

APB1 and APB2 are sourced from the AHB Protocol. and APB2 has 90MHz and APB1 supports upto 45MHz

All the peripherals are mostly connected with the APB1 and APB2 buses

Whereas GPIO is completely connected to AHB1 v Protocol

USB and CAMERA Interfaces are connected with AHB2 Bus which is also 180MHz high performing bus

AHB Bus Matrix also called as Engine of MCU

Common Important Points

- System Bus is not connected to FLASH Memory

- Processor can fetch instructions from FLASH over I-BUS

- Processor also can Fetch instructions from SRAM with I-BUS

- SRAM is connected to Processor to system bus over AHB Bus Matrix

- Processor cannot fetch both data and instructions both same time in SRAM (though only System Bus is there to communication with SRAM

- But Processor can communicate instruction and data and same time with FLASH with IBUS and DBUS

- Processor can talk with FLASH and SRAM simultaneously